Verilog Examples - Clock Divide by 4.5

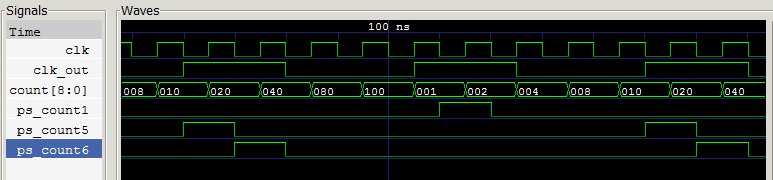

It is possible to generate a clock divided by 4.5 or for that matter any number like N+1/2. It involves some math. In this example we will use a ring counter that counts on the positive edge of clock.

We then use some counters at negative edges. The counters that we need is dictated by Math.

One advantage of the method we present below is that it does not create multilexers and hence is free from glithes. It however does not have 50% duty cycle.

Problem - Write verilog code that has a clock and a reset as input. It has an output that can be called clk_out. The clk_out is also a clock that has a frequency 4.5 times the frequency of the input clock. It has a negative reset input.

Solution -

This is the main code clock.v

|

Here is the test bench clocktb.v

|

Here is the result of the simulation count of the number of positive and negative pulses. for N=7.

Explanation 1. A ring counter is implemmented using

begin count <= count << 1; count[0] <= count[8]; end |

If you look at the counters in the code, you need to check the time periods of the OR of the followin two sets

count[0] | count[1] | ps_count1

and

ps_count5 | ps_count6| count[5]);