Interview Questions in Verilog

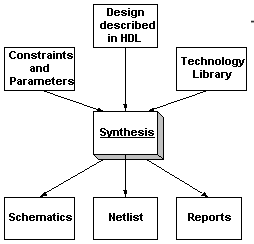

21. What do you mean by logic synthesis?Logic synthesis is mechanism by which RTL description is converted in terms of logic gates by the use of synthesis tool. It is recommended that signal width and variable width is explicitly specified. Defining unsized variable results in large gate level netlist.

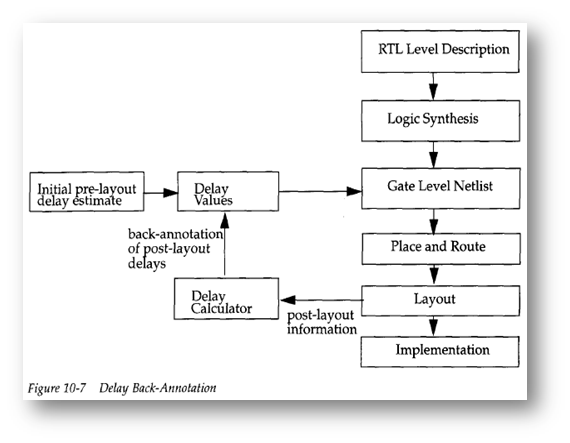

22. Show delay back annotation flow?

The above process is used repeatedly to obtain final circuit that meets timing requirements. 23. What is specparam?

Specparam provides mechanism to specify parameters inside specify block.This is different from module parameters which is not specified in specify block.

The following example illustrates specparam declarations:

specify specparam tRise_clk_q=150, tFall_clk_q=200; specparam tRise_control=40, tFall_control=50; endspecify |

24. What is PLI?

PLI is programmining language interface.Essentialy it’s a mechanism to invoke C function inside Verilog. It extends Verilog capabilities by allowing users to define their own utilities.Designers can write their own syatem tasks by using PLI routine.Some PLI application include

a. Application software like calculator or translator can be written using PLI.

b. Can be used to define customized system tasks and routines.

c. PLI can be used for customized output display

d. It allows users to change internal data structure.

25. What is force and release?

These are the second form of procrdural continuous assignment.They are used to force and release certain values to registers or nets.They are not used in design block and only used in stimulus block or testbench.They are active for certain period only.

The below example shows the use of force and release

module testbench; //statements Dff tdff(q,q_bar,d,clk,rst); initial begin #50 force tdff.Q = 1'b1; //Force Q to 1 at time 50 #50 release tdff.Q; //relaese Q at time 100 end //statements endmodule |

26. What is level sensitive timing control in Verilog?

We know that @ is used for edge sensitive timing control but Verilog also provides level sensitive timing control ie processor waits for certain expression or condition to be true to excute the statement.This is provided by “wait” statement.

Syntax:-

wait (expression) statement

Here expression is Boolean value ie true or false.When true statement is excuted.When false it waits for expression to become true.

27. What are types of compiler directives?

There are four types of compiler directives in Verilog

a. `define

b. `include

c. `ifdef

d. `timescale

`define is used to define text macros

For example:-

`define SIZE 16 `include is used to import entire Verilog file to another file.

For example if want to include moniter.v file into design.v

//design.v file

`include moniter.v

statements`ifdef directive checks if the macro has been defined or not if defined

It compliles the code that follows otherwise compiler compiles the code following an optional `else directive

`ifdef SIZE

`timescale directives specify time unit and time precision of module that follows it.

Syntax:

`timescale unit\precision

28. What is logic synthesis?

Logic synthesis is the mechanism to convert RTL description in terms of gate level representation.The main concern in logic synthesis are fanin,fanout etc.It can be technology dependent or technology independent.Logic synthesis tools are present for this purpose.

29. Write a Verilog code to swap contents of two register with and without temporary registers.

//with temporary register always @(posedge clk) begin temp = b; b = a; temp = a; end //without temporary register always @(posedge clk) begin a<=b;b<=a; end |