casez and casex |

In addition to the regular case statements, verilog provides two variations casez and casex. Before we try to understand casex and casez, we need to understand that there are 4 types of logic levels and in verilog

0 - logic zero

1 - logic one,

z - high impedance state.

x - unknown logic value - can be 0,1,z or transition.

In normal case statement, the case expression needs to EXACTLY match, for one of the case statements to execute. There is no provision of Don't cares.

casez solves this problem by allowing dont cares. If there is a z or ? in the case expression, then it means that the expression can match to 0, 1 or z.

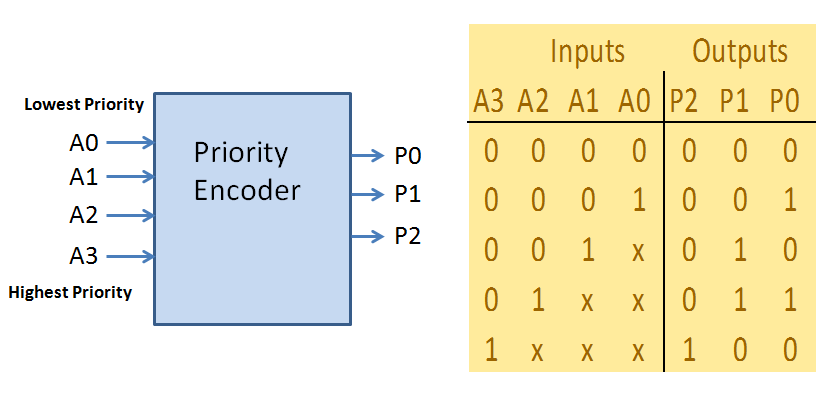

A very good example is the priority encoder. A common use of priority encoders is for interrupt controllers, where we select the most critical out of multiple interrupt requests.

Here is the truth table and block diagram of a 4 input and 3 output priority encodr.

|

Note the statement

4'b1zzz :

pcode = 3'b100;

It means that we don't care if the bits [2:0] are 0, 1 or z. The above statement could also be written as

4'b1??? :

pcode = 3'b100;

We now suggest that you write a test bench for this code and verify that it works. If you have difficulty, you can check it with following test bench

|

As another example consider a multiplexer, that has 4 input bits and one output bit. The output is connected to one of the inputs depending upon the value of the input bits. Normally you will need only 2 select bits but we have used 3 select bits. Why ?

|

If the MSB select bit is 1, the output is forced to 0 no matter what.

Another thing to notice is that, when more there is more than one match, the first match takes effect. Let us say we have the code.

|

It gives the following output

Driving 0

CASEZ : Logic z on select

Driving 1

CASEZ : Logic z on select

Driving z

CASEZ : Logic z on select

The reason is that the first case statement

1'bz : $display("CASEZ : Logic z on select");

which is equivalent to

1'b? : $display("CASEZ : Logic z on select");

gets selected no matter what the dont care input is - 0,1 or z

However, if we change the order of the case assignment statement as in

|

The output changes to

Driving 0

CASEZ : Logic 0 on select

Driving 1

CASEZ : Logic 1 on select

Driving z

CASEZ : Logic 1 on select

The casex is same as the casez execpt that the don't care also include x in addition to 0,1 and z. This is usually helpful in simulation, when we can give out value x to the module and test for the output.

| Exercise |

1. .